### EM Microelectronic-Marin SA A Company of SMH

EM Microelectronic-Marin S.A.'s production and design facilities in Marin / Neuchâtel

#### History

Microelectronic-Marin was founded in 1975 as a division of the Swiss Ebauches Electronics S.A., which was a member of the ASUAG group of companies. It was the first major step this large Swiss watch manufacturing group took into the world of sophisticated microelectronics. Almost 10 years later this group merged with the SSIH group to form the new SMH, the largest Swiss group of companies manufacturing watches and microelectronics.

At the same time, the Microelectronic-Marin division was formed into an independent company, EM Microelectronic-Marin SA. With strong financial backing from this large industrial group, it has successfully developed into a leading position and is now considered one of the world's leading low-power, low-voltage CMOS manufacturers, 100% financed by Swiss capital. Investing enormous effort into research and development as well as into the continuous up-dating of production methods and equipment, EM has reached a high technological stand-

ard in low-power, low-voltage CMOS technology, which has been the key to the success of its products. Considering that integrated circuits have not only innovated watches and computers, but also dominate machine controls, industrial robots, medical, measuring, and chemical instrumentation, as well as processing controls, telecommunications, toys, and entertainment products, it has been a logical step forward for EM to increasingly expand its semiconductor activities from watch ICs into the field of industrial circuits. EM is striving to become a major supplier in the field of user-specific, customized and standard low-power, low-voltage CMOS circuits for the electronics industry, putting its design capabilities and its specific advanced technologies to good use. However, being one of the world's leading manufactu-

However, being one of the world's leading manufacturers of watch circuits, with a world market share of over 20% in analog watch ICs, EM will also continue to grow in this. its traditional. market.

## **Table of Contents**

| General Information                       | 1  |

|-------------------------------------------|----|

| Quality Assurance and Reliability         | 2  |

| Display Driver                            | 3  |

| Real Time Clock                           | 4  |

| Watch                                     | 5  |

| Watchdog                                  | 6  |

| Smart Reset                               | 7  |

| Regulator and Surveillance Functions      | 8  |

| Interface                                 | 9  |

| Contactless Identification Devices, CID   | 10 |

| EMS Mixed-Mode Arrays                     | 11 |

| Other Services                            | 12 |

| Ordering Information                      | 13 |

| Offices, Distributors and Representatives | 14 |

### **Important Notice**

EM Microelectronic-Marin SA cannot assume responsibility for use of any circuitry described other than circuitry entirely embodied in an EM Microelectronic-Marin SA product. EM Microelectronic-Marin SA reserves the right to change the circuitry and specifications without notice at any time. You are strongly urged to ensure that the information given has not been superseded by a more up-to-date version.

## **General Information**

| Table of Contents                        | Page   |

|------------------------------------------|--------|

| Quality Policy                           | 1- 3   |

| Selection Guide                          |        |

| Display Driver                           | 1 - 4  |

| Real Time Clock                          | 1 - 5  |

| Watch                                    | 1 - 7  |

| Watchdog                                 | 1 - 8  |

| Smart Reset                              | 1 - 10 |

| Regulator and Surveillance Functions     | 1 - 13 |

| Interface                                | 1 - 16 |

| Contactless Identification Devices (CID) | 1 - 17 |

| EMS Mixed-Mode Arrays                    | 1 - 18 |

## **Quality Policy**

#### EM MICROELECTRONIC-MARIN SA

Une société de SME

#### QUALITY POLICY

BY TOTAL COMMITMENT WE WILL IMPROVE TOWARDS THE HIGHEST QUALITY FOR PRODUCTS AND PROVIDE SERVICES THAT MEET OR EXCEED THE REQUIREMENTS OF OUR CUSTOMERS AND THE STANDARDS OF OUR COMPETITION.

The mission shall be accomplished within the framework of five underlying principles for continued emphasis on quality that shall guide company objectives, plans and activities.

- 1. Our aim is the total satisfaction of our customers' needs.

- 2. Management fixes the goals and supports the actions of quality improvement.

- 3. Quality is everyone's job.

- 4. Our goal is "zero defects".

- 5. We do it right the first time.

Quality & Reliability Manager

ront End Operations Manager

M. Muss.

President & General Manager

Rev. B / 26.11.90

### **Display Driver**

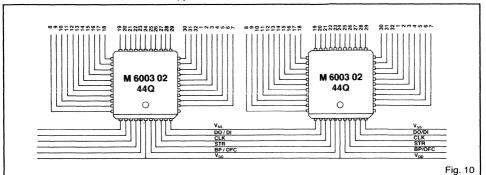

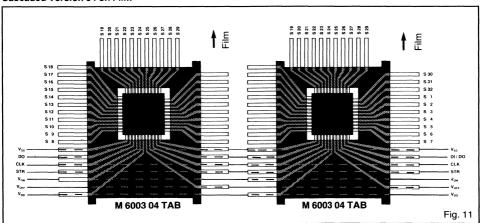

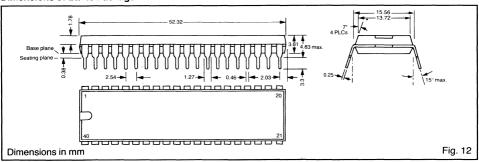

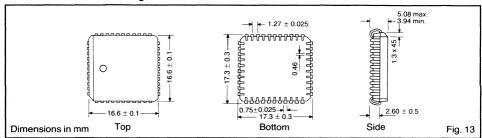

| ЕМ Туре   | Features                                                                                                                                                                                                                                                                                                                                                                                                                             | Applications                                                                        | Supply<br>Voltage                                  | Typ. current<br>Consumption | Package         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------|-----------------|

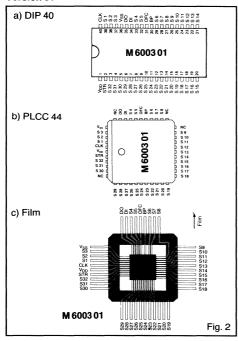

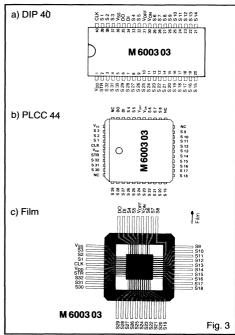

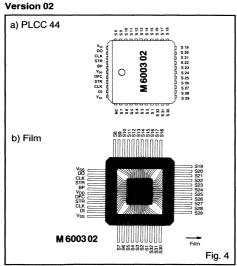

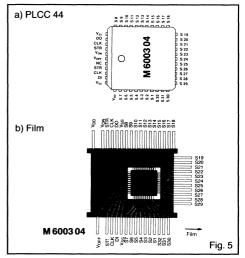

| M 6003 01 | Static LCD Driver, any layout     1-bit interface     32 segments     On-chip oscillator                                                                                                                                                                                                                                                                                                                                             | Automotive<br>displays<br>Utility meters<br>Balances<br>Battery powered<br>products | $3 \le V_{DD} \le 15 V$                            | 1.5 μA at 5 V               | DIP40<br>PLCC44 |

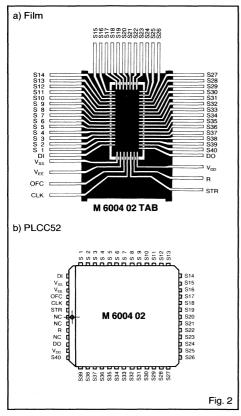

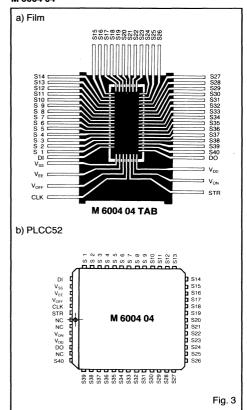

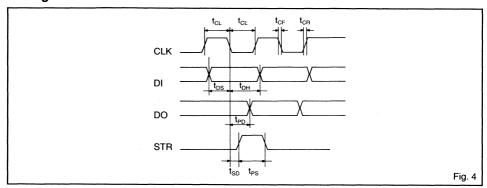

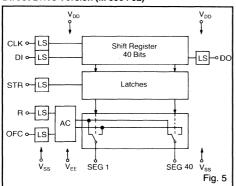

| M 6004 02 | Static LCD Driver, any layout     1-bit interface     40 segments     Crossfree cascadable                                                                                                                                                                                                                                                                                                                                           | Automotive<br>displays<br>Utility meters<br>Balances<br>Battery powered<br>products | $V_{DD}: 5 V \pm 10\%$<br>$5 \le V_{LCD} \le 12 V$ | 10 μA max. at 5 V           | PLCC52          |

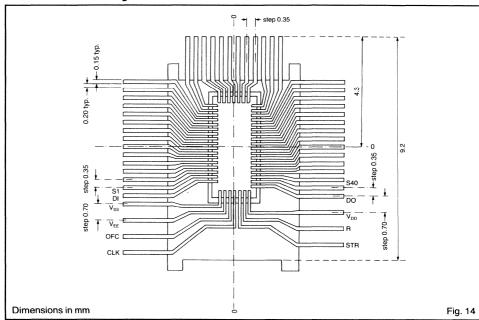

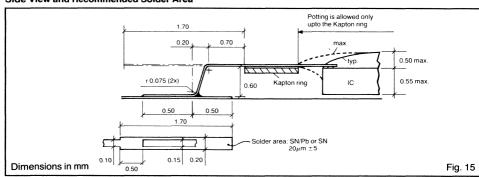

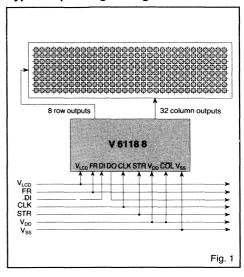

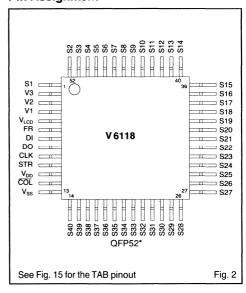

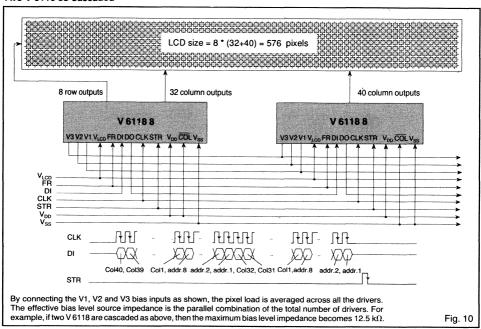

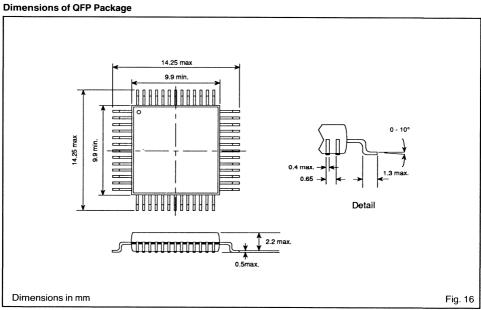

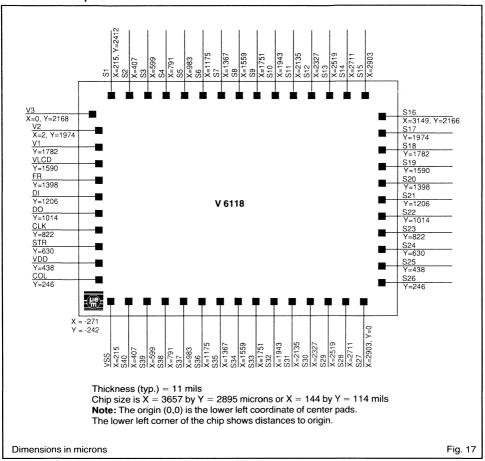

| V 6118 8  | Multiplex LCD Driver, any layout     1-bit interface     8-way max. (8 rows, 32 columns)     Standby current: typ. 100 nA at 5 V     Crossfree cascadable     Independent LCD supply voltage     Waveforms generated on chip, no external components required     Display refresh on chip, 8 x 40     RAM for display storage     Column driver only mode     LCD updating synchronized to the LCD refresh signal     BLANK function | Automotive<br>displays<br>Utility meters<br>Balances<br>Pagers                      | $2 \le V_{DD} \le 6V$ $2 \le V_{LCD} \le 7V$       | 100 μA at 7 V               | QFP52<br>TAB    |

| 4         | Same as V6118 8 except:  • 4-way mux (4 rows, 36 columns)  • 4 x 40 RAM for display storage                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                                                    |                             | QFP52<br>TAB    |

| 2         | Same as V6118 8 except:  • 2-way mux (2 rows, 38 columns)  • 2 x 40 RAM for display storage                                                                                                                                                                                                                                                                                                                                          |                                                                                     |                                                    |                             | QFP52<br>TAB    |

### **Real Time Clock**

| ЕМ Туре | Features                                                                                                                                                                                                                                                                                                                                                                                                                              | Applications                                                                                                        | Supply<br>Voltage                                                        | Typ. Current<br>Consumption      | Package        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------|----------------|

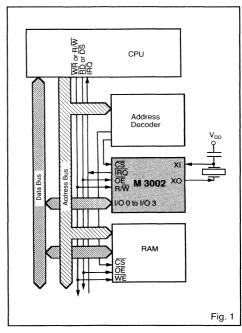

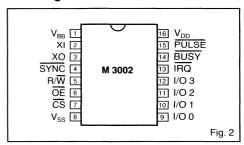

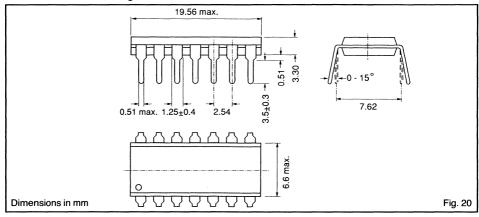

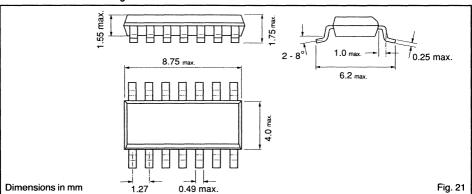

| M 3002  | ■ RTC, 4-bit interface ■ 32 kHz quartz oscillator ■ Clock: counts from seconds to 99 years ■ Alarm: counts from seconds to 31 days ■ Timer: counts from seconds to 24 hours ■ Low current consumption: typ. 5 μA at 3 V ■ Access time 150 ns typical ■ Battery pin                                                                                                                                                                    | POS terminals<br>Telecom systems<br>Control systems<br>Data loggers                                                 | $2.4 \leq Bat. \leq 5.0 \text{ V} \\ 2.4 \leq V_{DD} \leq 5.5 \text{ V}$ | 6 μA at 5 V<br>5 μA at 3 V       | DIP 16<br>SO16 |

| M 3003  | ■ RTC, 4-bit interface ■ 32 kHz quartz oscillator ■ Clock: counts from seconds to 99 years ■ Alarm: counts from seconds to 31 days ■ Timer: counts from seconds to 24 hours ■ Low current consumption: typ. 5 μA at 3 V ■ Access time 150 ns typical ■ Power fail connection                                                                                                                                                          | POS terminals<br>Telecom systems<br>Control systems<br>Data loggers                                                 | $2 \le V_{DD} \le 5.5 V$                                                 | 12 μA at 5 V<br>5 μA at 3 V      | DIP16<br>SO16  |

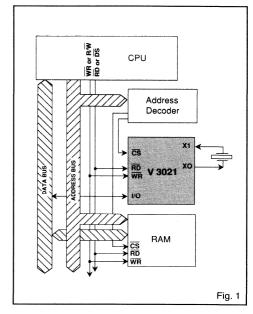

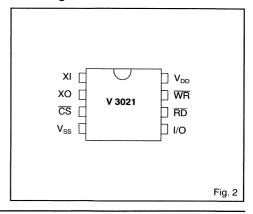

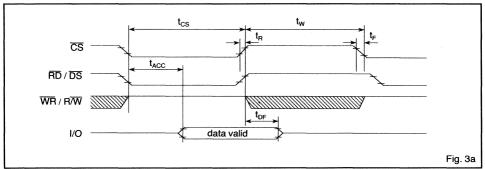

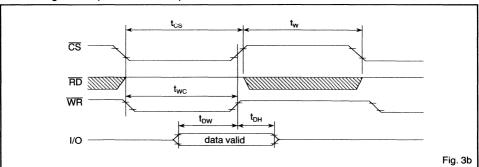

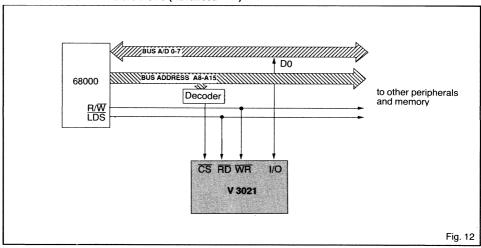

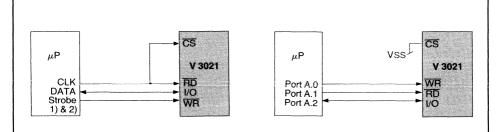

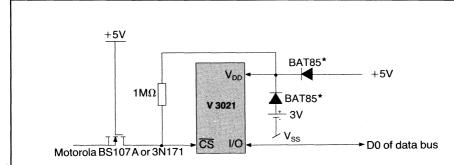

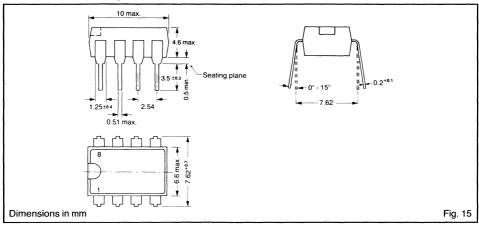

| V 3021  | RTC, 1-bit interface     32 kHz quartz oscillator     Very low current consumption: typ, 800 nA at 3 V     Max. 60 ns access time     No busy states     Clock: counts from seconds to 99 years     No external capacitor required                                                                                                                                                                                                    | White/Brown<br>goods<br>Pay phones<br>POS terminals<br>Hand-held<br>systems                                         | $2 \le V_{DD} \le 5.5 V$                                                 | 800 nA at 3 V<br>1.3 μA at 5.5 V | DIP8<br>SO8    |

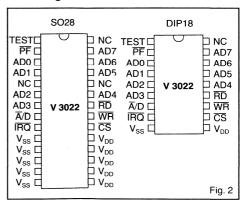

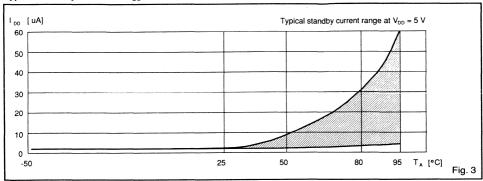

| V 3022  | RTC, 8-bit interface Built-in 32 kHz crystal with digital trimming and temperature compensation facilities Sleep mode current consumption: typ. 1.2 µA at 3 V Max. 60 ns access time Universal interface compatible with both Intel and Motorola No busy states Power fail input BUS can be tri-state when PF active 12 or 24 hours data formats Time to 1/100 of a second Programmable interrupts Alarm programmable up to one month | Industrial<br>controllers<br>Alarm systems<br>PABX and tele-<br>com systems<br>Hand-held<br>systems<br>Data loggers | $2 \le V_{DD} \le 5.5 V$                                                 | 1.2 μA at 3 V<br>2 μA at 5.5 V   | DIP18<br>SO28  |

### **Real Time Clock**

| ЕМ Туре | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Applications                                                                                                        | Supply<br>Voltage        | Typ. Current Consumption       | Package       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------|---------------|

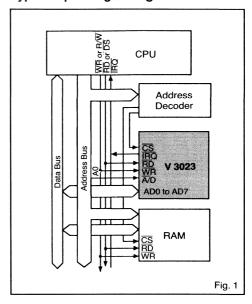

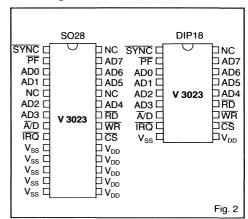

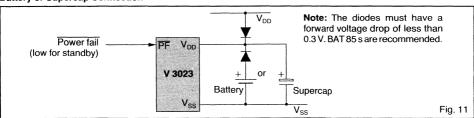

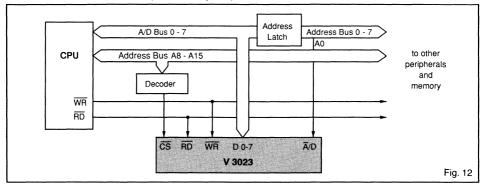

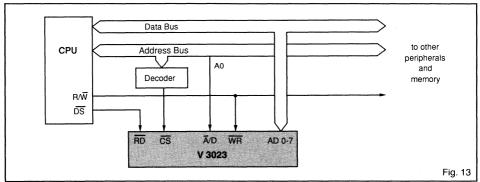

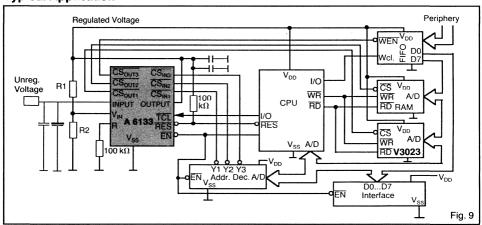

| V 3023  | RTC, 8-bit interface Built-in 32 kHz crystal with digital trimming and temperature compensation facilities 16 bytes of user RAM Can be synchronized to 50 Hz or nearest sec./min. Sleep mode current consumption: typ. 1.2 µA at 3 V Max. 60 ns access time Universal interface compatible with both Intel and Motorola No busy states Power fail input BUS can be tri-state when PF active 12 or 24 hours data formats Time to 1/100 of a second Programmable interrupts Alarm programmable up to one month | Industrial<br>controllers<br>Alarm systems<br>PABX and tele-<br>com systems<br>Hand-held<br>systems<br>Data loggers | $2 \le V_{DD} \le 5.5 V$ | 1.2 μA at 3 V<br>2 μA at 5.5 V | DIP18<br>SO28 |

### Watch

| ЕМ Туре        | Features                                                                                                                                                                                                                                   | Applications          | Supply<br>Voltage           | Typ. Current<br>Consumption   | Package      |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|-------------------------------|--------------|

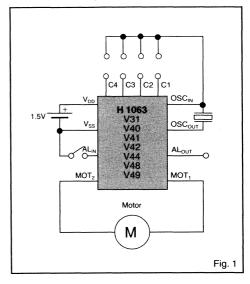

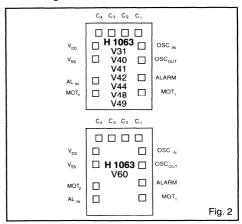

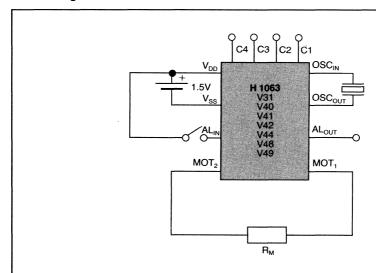

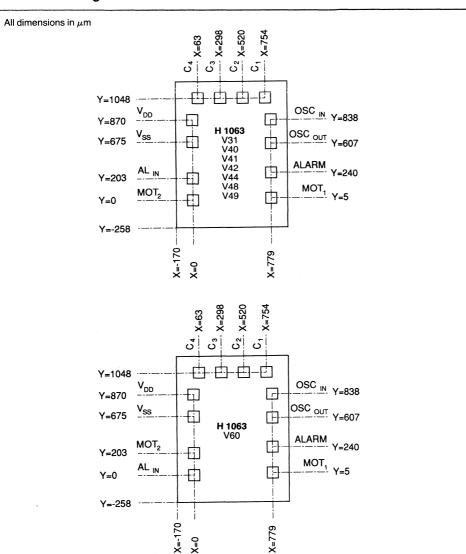

| H 1063         | 32 kHz quartz oscillator     Digital trimming     Low current consumption:     typ. 800 nA     Low output impedance for bipolar     stepping motor     Programmable alarm functions                                                        | Analog clocks         | $1.1 \le V_{DD} \le 1.8  V$ | 2 μA max. at 1.8 V            | CHIP         |

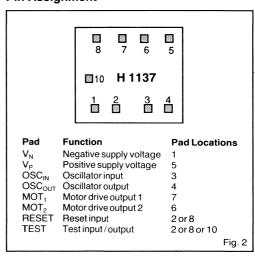

| H1137          | 32 kHz quartz oscillator     High oscillator stability     Very low current consumption: typ. 250 nA     Low output impedance for bipolar stepping motor     Programmable motor period and motor pulse width  Mirror version of the H 1127 | Analog<br>watches     | $1.2 \le V_{DD} \le 1.8  V$ | 350 nA max.<br>at 1.55 V      | CHIP         |

| H 1127         | Mirror version of the H 1137                                                                                                                                                                                                               | <u> </u>              |                             |                               |              |

| H 1344         | <ul> <li>32 kHz quartz oscillator</li> <li>Low current consumption:<br/>typ. 700 nA</li> <li>Low output impedance for bipolar<br/>stepping motor</li> <li>Programmable alarm functions</li> </ul>                                          | Analog clocks         | $1.1 \le V_{DD} \le 1.8 V$  | 2 μA max. at 1.8 V            | CHIP<br>DIP8 |

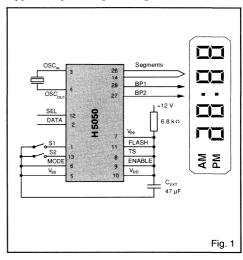

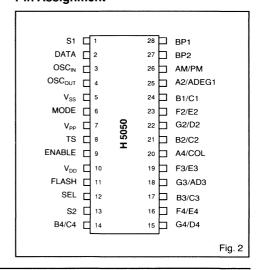

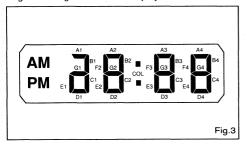

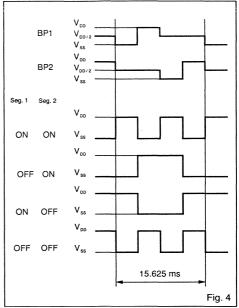

| H 5050         | 4,19 MHz quartz oscillator     LCD BIAS voltages:     - adjustable via E <sup>2</sup> PROM     - with temperature compensation     12 or 24 hour display mode     High electromagnetic immunity                                            | Digital car<br>clocks | $3 \le V_{DD} \le 6 V$      | 700 $\mu$ A at $V_{DD} = 5 V$ | SO28         |

| 1H<br>2H<br>4H | 1 Hz auto-increment<br>2 Hz auto-increment<br>4 Hz auto-increment                                                                                                                                                                          |                       |                             |                               |              |

### Watchdog

| ЕМ Туре                    | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applications                                                                                                | Supply<br>Voltage                   | Typ. Current<br>Consumpt.                     | Package       |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------------------------------|---------------|

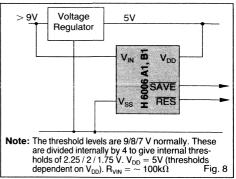

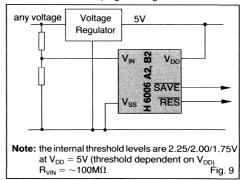

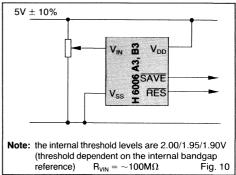

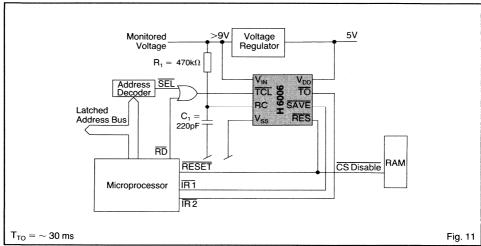

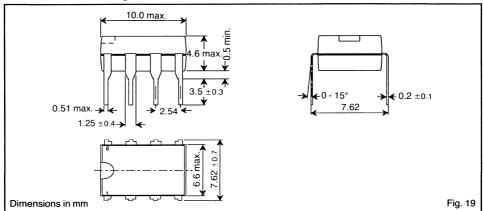

| A2<br>A3<br>B1<br>B2<br>B3 | Low voltage alarm prior to reset     Automatic reset initialized on power-up     Remains in reset after timeout - Fail safe     Outputs guaranteed down to V <sub>DD</sub> = 1.5V     Standard timeout period (10 ms) or     externally programmable  Monitored Voltage Thresholds (V)     Open drain outputs     2.25, 2.00, 1.75 at V <sub>DD</sub> = 5 V     2.00, 1.95, 1.90 independent from V <sub>DD</sub> Push-pull outputs     9.00, 8.00, 7.00 at V <sub>DD</sub> = 5 V     2.25, 2.00, 1.75 at V <sub>DD</sub> = 5 V     2.00, 1.95, 1.90 independent from V <sub>DD</sub> | POS terminals<br>Automotive<br>electronics<br>White goods                                                   | $1.5 \le V_{DD} \le 5.5 V$          | 50 μA at 5 V                                  | DIP8<br>SO8   |

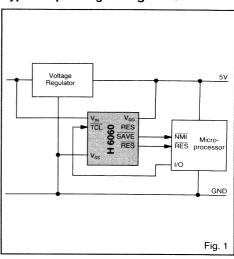

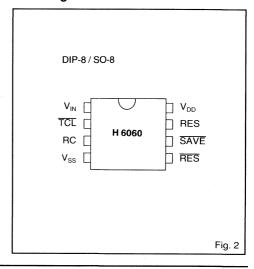

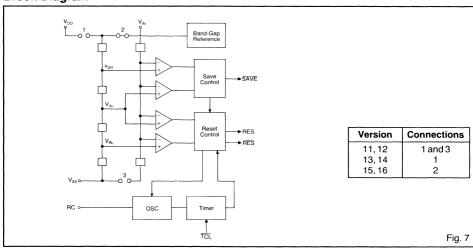

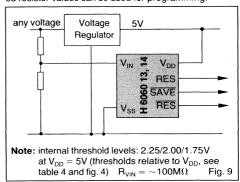

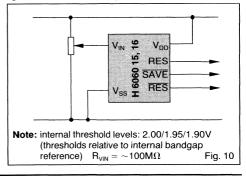

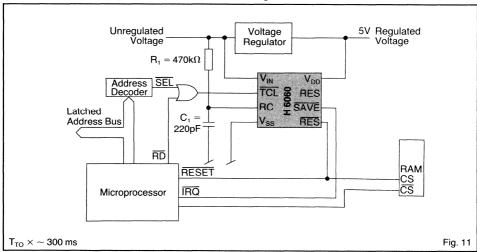

| H 6060<br>14<br>16<br>15   | Low voltage alarm prior to reset     Automatic reset initialized on power-up     Self-recovering reset after timeout     Outputs guaranteed down to V <sub>DD</sub> = 1.6V     Standard timeout period (100 ms) or     externally programmable     Monitored Voltage Thresholds (V)     Push-pull outputs     2.25, 2.00, 1.75 at V <sub>DD</sub> = 5 V     2.00, 1.95, 1.90 independent from V <sub>DD</sub> Open drain outputs     2.00, 1.95, 1.90 independent from V <sub>DD</sub>                                                                                                | POS terminals<br>Automotive<br>electronics<br>White goods                                                   | $1.6 \le V_{DD} \le 5.5 V$          | 80 μA at 5 V                                  | DIP8<br>SO8   |

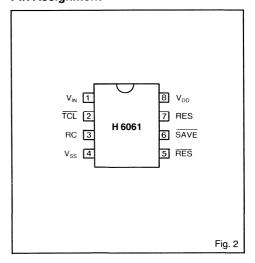

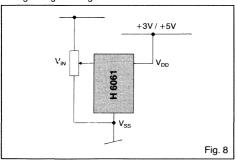

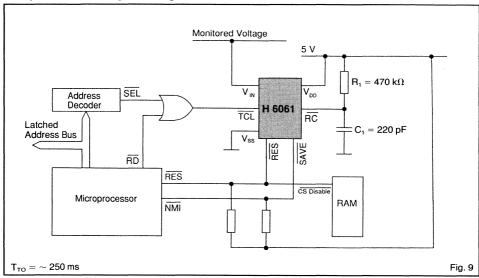

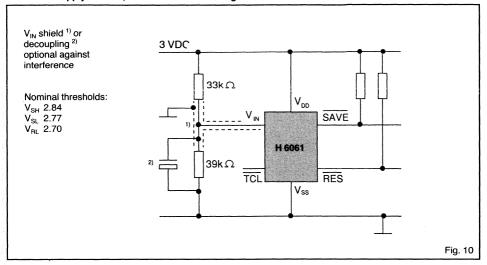

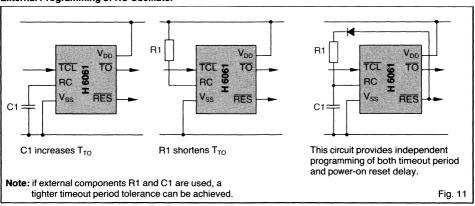

| H 6061                     | Low voltage alarm prior to reset     Automatic reset initialized on power-up     Self-recovering reset after timeout     Outputs guaranteed down to V <sub>DD</sub> = 1.6V     Standard timeout period (100 ms) or     externally programmable     Monitored Voltage Thresholds (V)     Open drain outputs     1.54, 1.50, 1.46 independent from V <sub>DD</sub>                                                                                                                                                                                                                      | POS terminals<br>Telephone<br>handsets<br>Modems                                                            | $2.7 \le V_{DD} \le 5.25 \text{ V}$ | 80 μA at 5 V                                  | DIP8<br>SO8   |

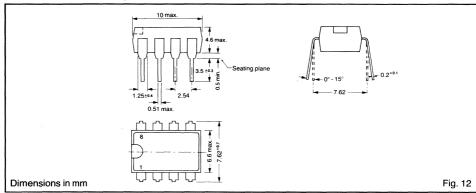

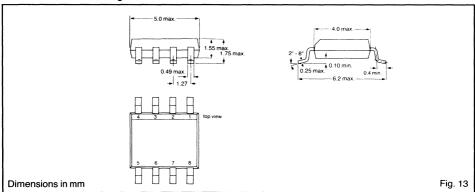

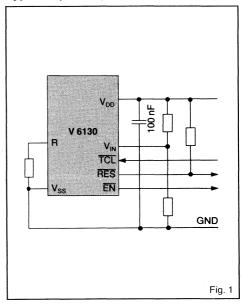

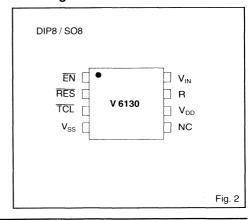

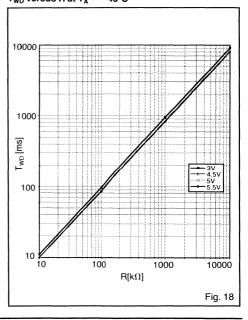

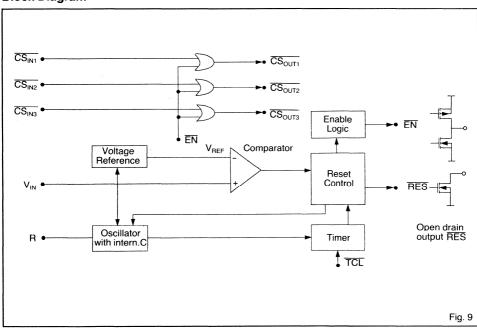

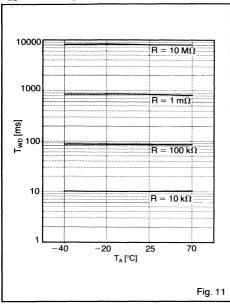

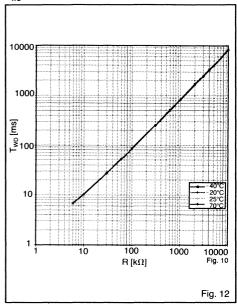

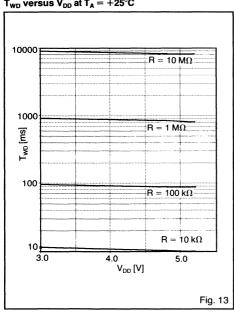

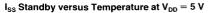

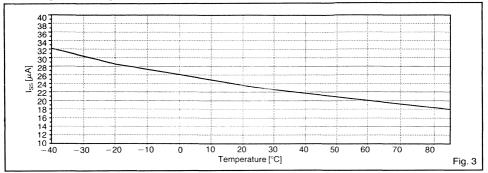

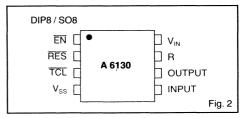

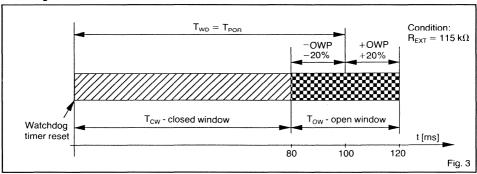

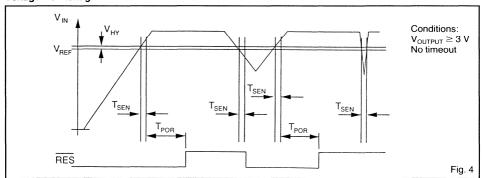

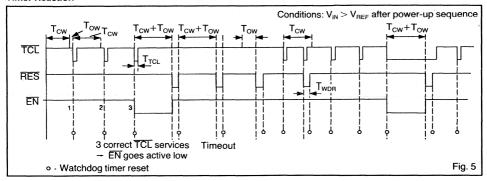

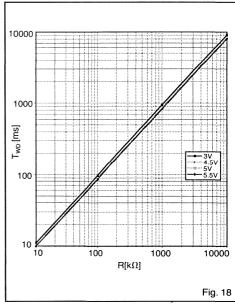

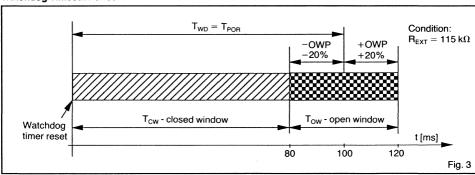

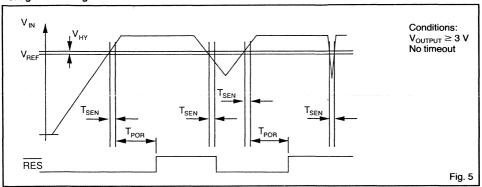

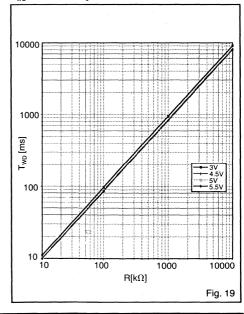

| V 6130                     | $ \begin{array}{l} \bullet \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Industrial<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products | $3 \le V_{DD} \le 5.5 V$            | $55 \mu$ A at $5.5 V$ with $R_{EXT} = 100 kΩ$ | DIP8<br>SO8   |

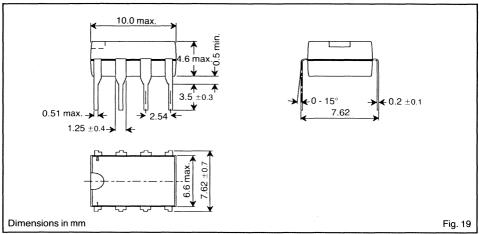

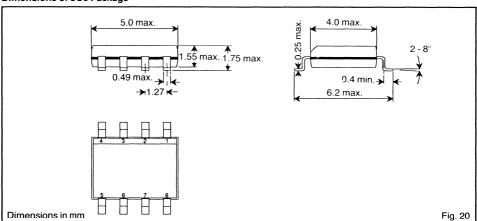

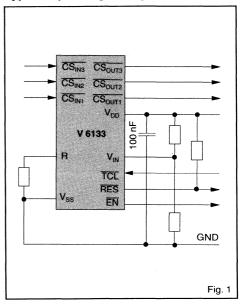

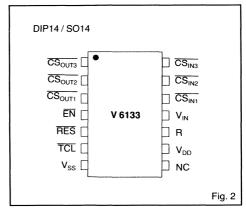

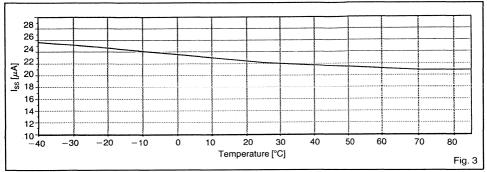

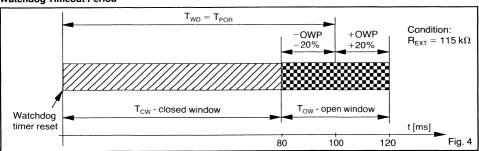

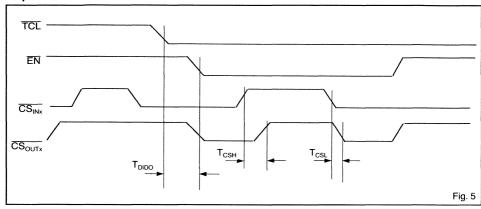

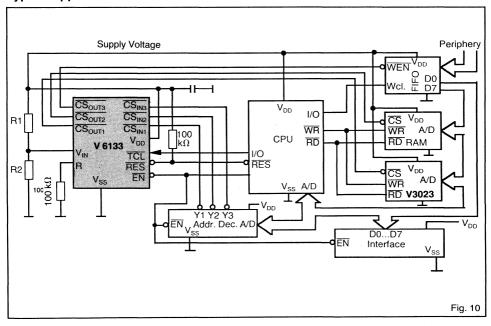

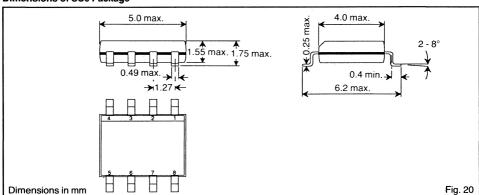

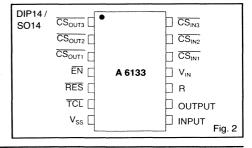

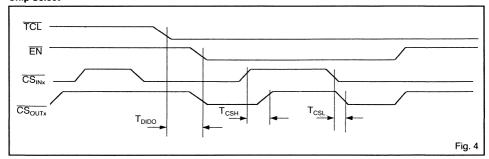

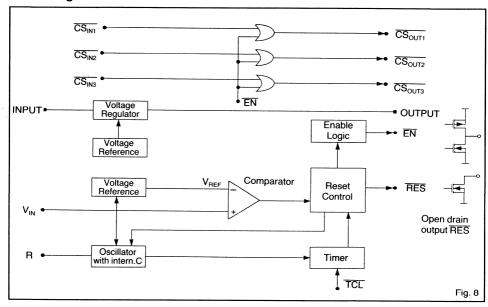

| V 6133                     | <ul> <li>Voltage and software monitoring</li> <li>3 chip select disable circuits</li> <li>Standby mode: typ. 22 μA at 5 V</li> <li>Reset output guaranteed down to V<sub>DD</sub> = 1.2 V</li> <li>Programmable reset threshold</li> <li>Voltage reference accuracy ± 1.5%</li> <li>Programmable delays for P.O.R. and W.D. windows</li> <li>Time base accuracy ± 10% (over the full temperature range)</li> <li>ENABLE function</li> <li>TTL/CMOS compatibility</li> </ul>                                                                                                           | Industrial<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products | $3 \le V_{DD} \le 5.5 V$            | $55 \mu$ A at $5.5 V$ with $R_{EXT} = 100 kΩ$ | DIP14<br>SO14 |

### Watchdog

| ЕМ Туре | Features                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applications                                                                                                | Supply<br>Voltage        | Typ. Current<br>Consumpt.                                                                                                  | Package       |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------|

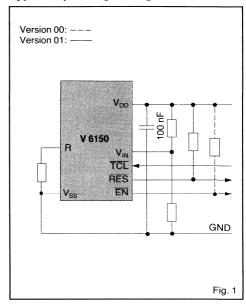

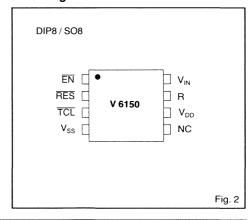

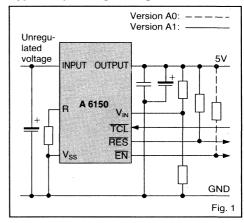

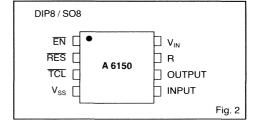

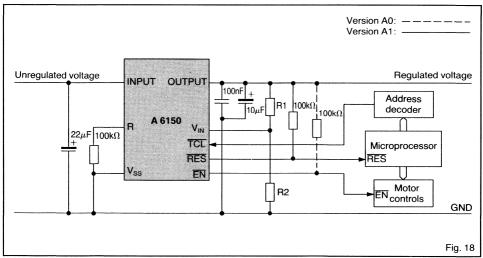

| V 6150  | • Voltage and software monitoring • Standby mode: typ. $23 \mu\text{A}$ at 5 V • Reset output guaranteed down to $V_{\text{DD}} = 1.2 \text{V}$ • Programmable reset threshold • Voltage reference accuracy $\pm  3\%$ • Programmable delays for P.O.R. and W.D. windows • Time base accuracy $\pm  10\%$ (over the full temperature range) • ENABLE function • TTL / CMOS compatibility $\overline{\text{EN}} = \text{push-pull}$ ; RES = open drain | Automotive<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products | $3 \le V_{DD} \le 5.5 V$ | $75 \mu\text{A}$ at 5.5 V with $R_{\text{EXT}} = 100 \text{k}\Omega$                                                       | DIP8<br>SO8   |

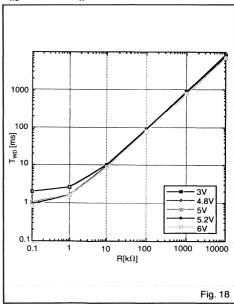

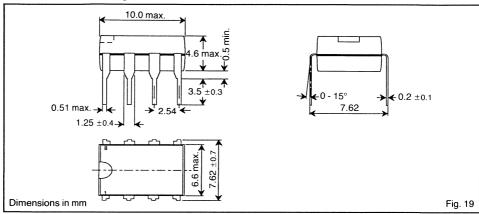

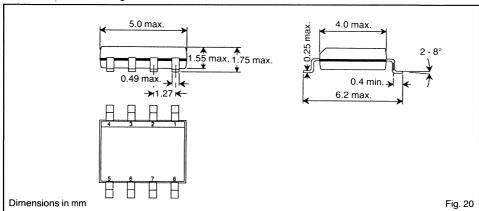

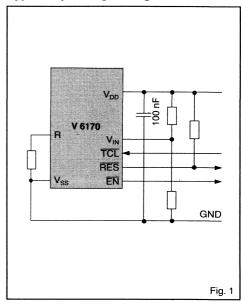

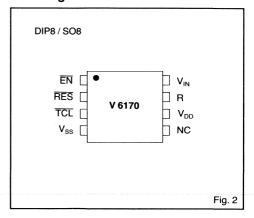

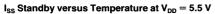

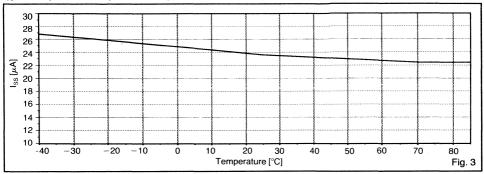

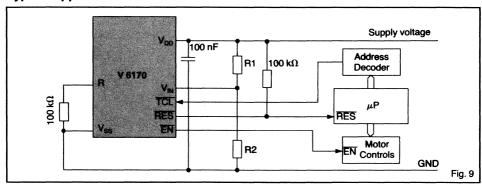

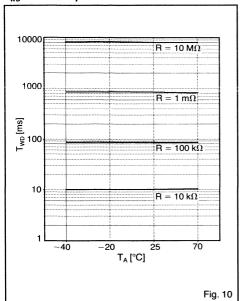

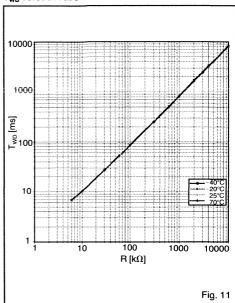

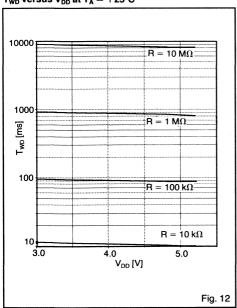

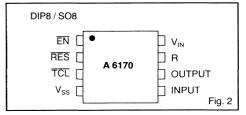

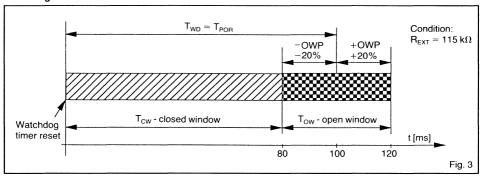

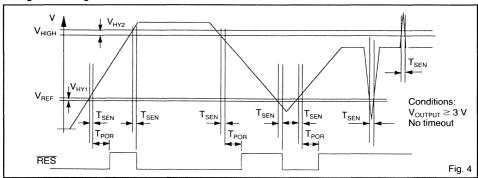

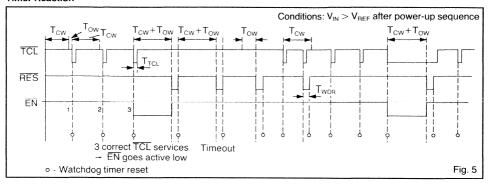

| V 6170  | $ \begin{array}{l} \bullet \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                                                                                                                                                                                                                      | Industrial<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products | $3 \le V_{DD} \le 5.5 V$ | $\begin{array}{l} 55\mu\text{A}\text{at}5.5\text{V}\\ \text{with}\\ \text{R}_{\text{EXT}} = 100\text{k}\Omega \end{array}$ | DIP8<br>SO8   |

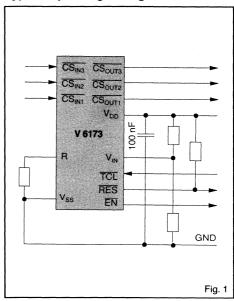

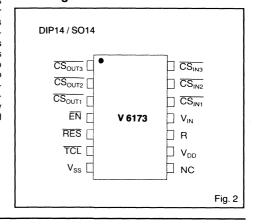

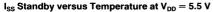

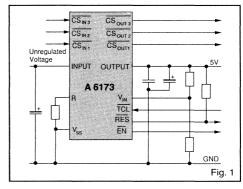

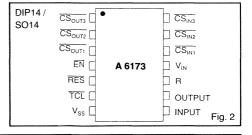

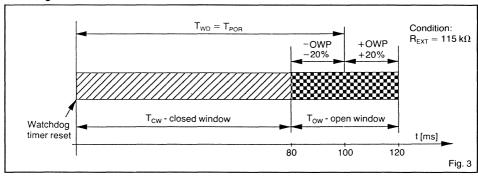

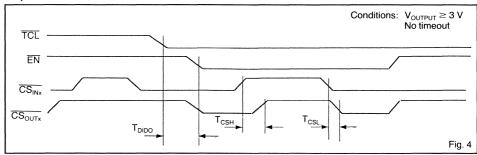

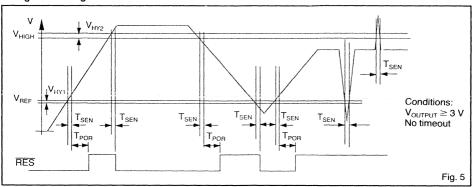

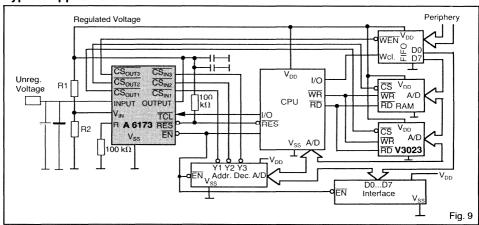

| V 6173  | Voltage and software monitoring chipselect disable circuits Standby mode: typ. 24 µA at 5 V Reset output guaranteed down to V <sub>DD</sub> = 1.2 V Programmable reset low threshold Voltage window, high threshold 5.9 V Voltage reference accuracy ± 1.5% Programmable delays for P.O.R. and W.D. windows Time base accuracy ± 10% (over the full temperature range) ENABLE function TTL/CMOS compatibility                                         | Industrial<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products | $3 \le V_{DD} \le 5.5 V$ | $55 \mu A at 5.5 V$ with $R_{EXT} = 100 kΩ$                                                                                | DIP14<br>SO14 |

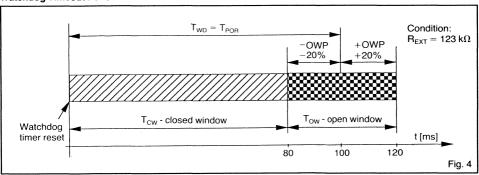

### **Smart Reset**

| ЕМ Туре                      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Applications                                                                                         | Supply<br>Voltage           | Typ. Current<br>Consumpt.                       | Package          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------|------------------|

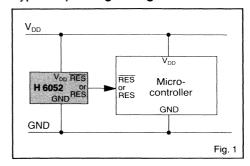

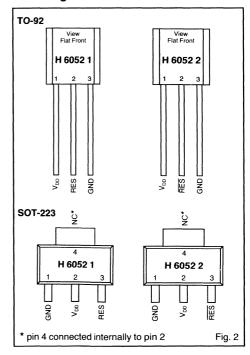

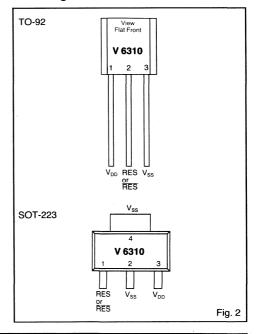

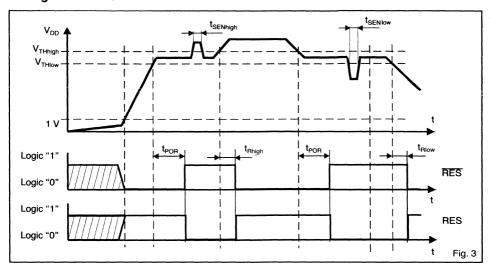

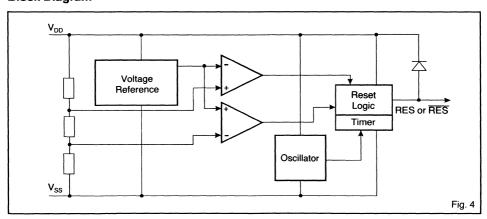

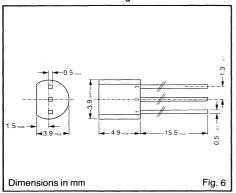

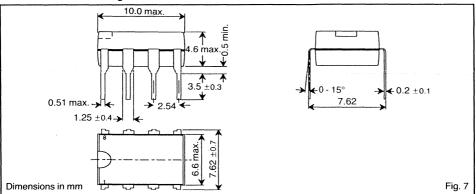

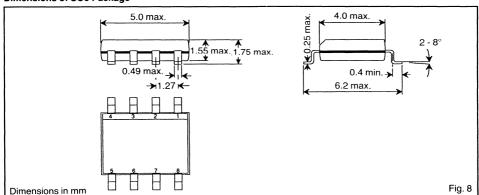

| H 6052                       | Clear microprocessor start on power-up Reset output guaranteed down to Vpp = 1.6 V On-chip oscillator No external components required Reset output Reset output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Automotive<br>electronics<br>White/Brown<br>goods<br>Industrial<br>systems                           | $1.6 \le V_{DD} \le 5.5  V$ | 80 μA at 5 V                                    | TO-92<br>SOT-223 |

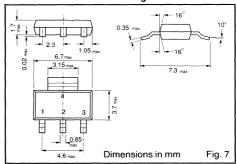

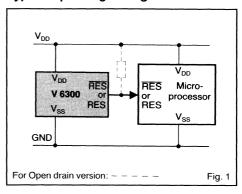

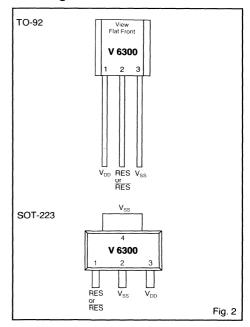

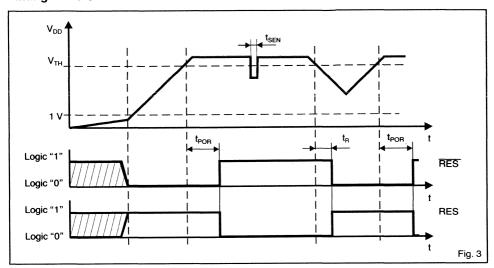

| V 6300  ABCDEF GHIJKL MNOPQR | <ul> <li>Clear microprocessor start on power-up</li> <li>Reset output guaranteed down to V<sub>DD</sub> = 1.0 V</li> <li>On-chip oscillator, no external components required</li> <li>Very low current consumption: 3.0 μA at 5 V</li> <li>Pin-out compatible with DS 1233A</li> <li>Monitored Voltage Thresholds</li> <li>Reset active low, push-pull 2.0 V¹¹</li> <li>2.4 V¹¹</li> <li>2.8 V¹¹</li> <li>3.5 V¹¹</li> <li>Reset active high, push-pull 2.0 V¹¹</li> <li>2.4 V¹¹</li> <li>2.8 V¹³</li> <li>3.5 V¹¹</li> <li>Reset active high, push-pull 2.0 V¹¹</li> <li>4.5 V¹¹</li> <li>Reset active low, open drain 2.0 V¹¹</li> <li>2.4 V¹¹</li> <li>2.8 V</li> <li>3.5 V¹</li> <li>Reset active low, open drain 2.0 V¹¹</li> <li>2.4 V¹¹</li> <li>2.8 V</li> <li>3.5 V¹</li> <li>4.0 V¹¹</li> <li>4.5 V¹¹</li> </ul> | Automotive<br>electronics<br>Industrial<br>electronics<br>Telecom<br>systems<br>Hand-held<br>systems | $1 \le V_{DD} \le 8V$       | 1.5 μA at 2 V<br>3.0 μA at 5 V<br>5.2 μA at 8 V | TO-92<br>SOT-223 |

<sup>1)</sup> Non-stock items, minimum order 30k pieces

#### **Smart Reset**

| ЕМ Туре                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Applications                                                                                         | Supply<br>Voltage      | Typ. Current<br>Consumpt.                       | Package          |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------|------------------|

| V 6310                      | Clear microprocessor start on power-up Reset output guaranteed down to V <sub>DD</sub> = 1.0 V On-chip oscillator, no external components required Very low current consumption: 3.0 µA at 5 V Pin-out compatible with DS 1233A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Automotive<br>electronics<br>Industrial<br>electronics<br>Telecom<br>systems<br>Hand-held<br>systems | $1 \le V_{DD} \le 8 V$ | 1.5 μA at 2 V<br>3.0 μA at 5 V<br>5.2 μA at 8 V | TO-92<br>SOT-223 |

| ABCDEF GI-JKL EZOPGR        | Monitored Voltage Windows  • Reset active low, push-pull 2.0 to 6 V¹¹ 2.4 to 6 V¹¹ 2.8 to 6 V¹¹ 4.0 to 6 V¹¹ 4.0 to 6 V¹¹ 4.5 to 6 V¹¹ 4.5 to 6 V¹¹ 2.8 to 6 V¹¹ 2.8 to 6 V¹¹ 2.8 to 6 V¹¹ 2.8 to 6 V¹¹ 3.5 to 6 V¹¹ 4.5 to 6 V¹¹ 2.8 to 6 V¹ 2.8 to 6 V¹ 3.5 to 6 V¹¹ 2.8 to 6 V¹ 4.5 to 6 V¹¹ |                                                                                                      |                        |                                                 |                  |

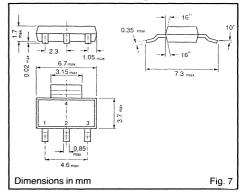

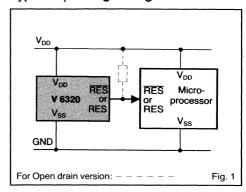

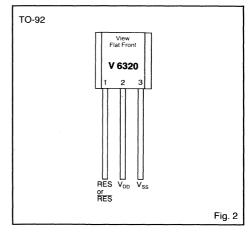

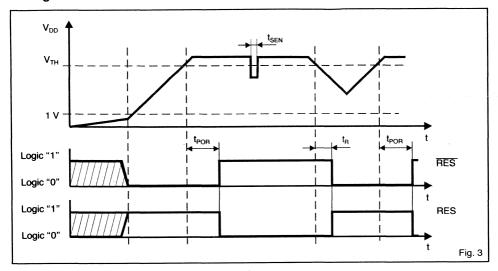

| V 6320 ABCDEF GHIJKL MNOPQR | Clear microprocessor start on power-up Reset output guaranteed down to V <sub>DD</sub> = 1.0 V On-chip oscillator, no external components required Very low current consumption: 3.0 µA at 5 V Pin-out compatible with MC 33064  Monitored Voltage Thresholds Reset active low, push-pull 2.0 V¹¹ 2.4 V¹¹ 2.8 V¹¹ 3.5 V¹¹ 4.0 V¹¹ 4.5 V¹¹  Reset active high, push-pull 2.0 V¹¹ 2.4 V¹¹ 2.8 V¹¹ 3.5 V¹ 4.0 V¹¹ 4.5 V¹¹  Reset active high, push-pull 2.0 V¹¹ 2.8 V¹¹ 3.5 V¹¹ 4.0 V¹¹ 4.5 V¹¹  Reset active low, open drain 2.0 V¹¹ 2.4 V¹¹ 2.8 V¹¹ 3.5 V¹ 4.0 V¹¹ 4.5 V¹  Reset active low, open drain 2.0 V¹¹ 2.8 V¹¹ 3.5 V¹ 4.0 V¹¹ 4.5 V¹  Reset active low, open drain 2.0 V¹¹ 2.8 V¹¹ 3.5 V¹ 4.0 V¹¹ 4.5 V¹  Reset active low, open drain 2.0 V¹¹ 2.8 V¹¹ 3.5 V¹ 4.0 V¹¹ 4.5 V                                                                                                                                   | Automotive<br>electronics<br>Industrial<br>electronics<br>Telecom<br>systems<br>Hand-held<br>systems | $1 \le V_{DD} \le 8 V$ | 1.5 μA at 2 V<br>3.0 μA at 5 V<br>5.2 μA at 8 V | TO-92            |

<sup>1)</sup> Non-stock items, minimum order 30k pieces

### **Smart Reset**

| ЕМ Туре                     | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Applications                                                                                  | Supply<br>Voltage             | Typ. Current<br>Consumpt.                            | Package |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------|------------------------------------------------------|---------|

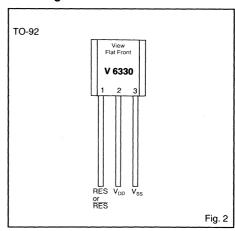

| V 6330  ABCCDEFGHIJKL MNOOP | Clear microprocessor start on power-up     Reset output guaranteed down to     V <sub>DD</sub> = 1.0 V     On-chip oscillator, no external components required     Very low current consumption:     3.0 μA at 5 V     Pin-out compatible with MC 33064  Monitored Voltage Windows     Reset active low, push-pull     2.0 to 6 V¹)     2.4 to 6 V¹)     4.5 to 6 V¹)     4.5 to 6 V¹)     4.5 to 6 V¹)     8. Reset active high, push-pull     2.0 to 6 V¹)     2.4 to 6 V¹)     3.5 to 6 V¹)     4.5 to 6 V¹)     8. Reset active high, push-pull     2.0 to 6 V¹)     2.4 to 6 V¹)     3.5 to 6 V¹)     4.5 to 6 V¹)     3.5 to 6 V¹)     4.5 to 6 V¹)     3.5 to 6 V¹)     4.5 to 6 V¹)     3.5 to 6 V¹)     4.5 to 6 V¹) | Applications  Automotive electronics Industrial electronics Telecom systems Hand-held systems | Voltage $1 \le V_{DD} \le 8V$ | Consumpt.  1.5 μA at 2 V 3.0 μA at 5 V 5.2 μA at 8 V | TO-92   |

| Q<br>R                      | 4.0 to 6 V <sup>1)</sup><br>4.5 to 6 V <sup>1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                               |                               |                                                      |         |

<sup>1)</sup> Non-stock items, minimum order 30k pieces

### **Regulator and Surveillance Functions**

| ЕМ Туре | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Applications                                                                                                                | Supply<br>Voltage                                                     | Typ. Current<br>Consumpt.                                              | Package       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|---------------|

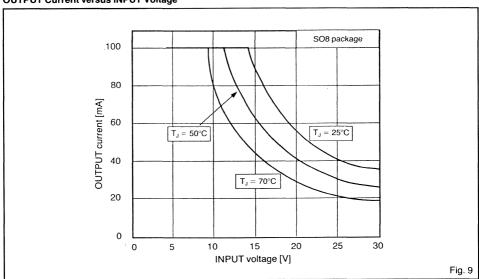

| A 6130  | <ul> <li>Voltage and software monitoring</li> <li>Standby mode: typ. 100 μA</li> <li>Highly accurate 5 V / 100 mA guaranteed output</li> <li>Low dropout voltage, typically 250 mV at 100 mA</li> <li>Unregulated voltage input can withstand – 20 V reverse battery and +60 V power transients</li> <li>Regulated voltage accuracy ± 1%</li> <li>Current limiting</li> <li>Reset output guaranteed down to V<sub>OUTPUT</sub> = 1.2 V</li> <li>Programmable reset threshold</li> <li>Voltage reference accuracy ± 1.5%</li> <li>Programmable delays for P.O.R. and W.D. windows</li> <li>Time base accuracy ± 10% (over the full temperature range)</li> <li>ENABLE function</li> <li>TTL/CMOS compatibility</li> </ul> | Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products<br>High efficiency<br>linear power<br>supply | $3.36 \le V_{\text{INPUT}} \le 26 \text{ V}$                          | 155 $\mu$ A at $V_{\text{INPUT}}$ = 6 V with $R_{\text{EXT}}$ = 100 kΩ | DIP8<br>SO8   |

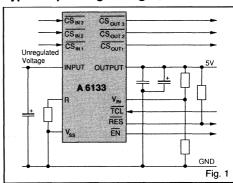

| A 6133  | Voltage and software monitoring Schip select disable circuits Standby mode: typ. 100 µA Highly accurate 5 V / 100 mA guaranteed output Low dropout voltage, typically 250 mV at 100 mA Unregulated voltage input can withstand –20 V reverse battery and +60 V power transients Regulated voltage accuracy ± 1% Current limiting Reset output guaranteed down to VOUTPUT = 1.2 V Programmable reset threshold Voltage reference accuracy ± 1.5% Programmable delays for P.O.R. and W.D. windows Time base accuracy ± 10% (over the full temperature range) ENABLE function TTL/CMOS compatibility                                                                                                                        | Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products<br>High efficiency<br>linear power<br>supply | $3.36 \le V_{INPUT} \le 26 V$                                         | 155 $\mu$ A at $V_{INPUT} = 6 V$ with $R_{EXT} = 100 k\Omega$          | DIP14<br>SO14 |

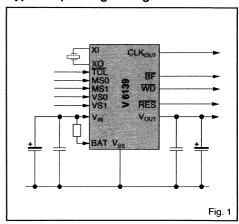

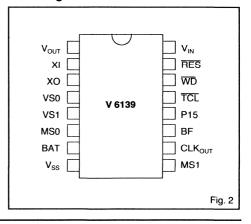

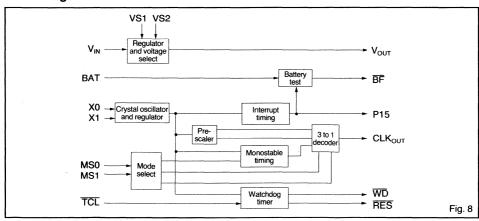

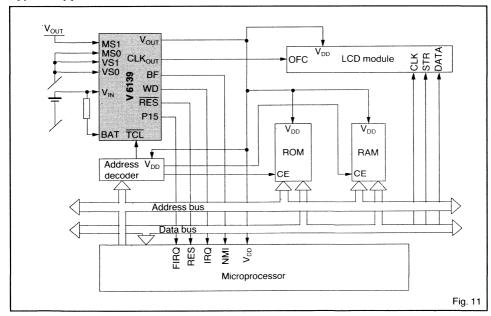

| V 6139  | Low power digitally programmable voltage regulator, 5 V, 3 V, or 2 V     Supply current 12 μA max. with: V <sub>IN</sub> = 10 V, V <sub>OUT</sub> = 5 V, I <sub>L</sub> = 50 mA     Low dropout voltage, 4 mV at I <sub>L</sub> = 100 μA     Short circuit and thermal protection     Battery fail warning, regulator input tested     Reset guaranteed down to V <sub>OUT</sub> = 1.5 V     32 kHz crystal oscillator, high stability     No external capacitor required with crystal                                                                                                                                                                                                                                   | Pagers and<br>cordless<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products                                | $ 2 \le V_{IN} \le 10 \text{ V} $ $ 1.5 \le V_{OUT} \le 6 \text{ V} $ | 7 μA at 7 V                                                            | DIP16<br>SO16 |

### **Regulator and Surveillance Functions**

| ЕМ Туре | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Applications                                                                                                                                             | Supply<br>Voltage                            | Typ. Current<br>Consumpt.                                                                              | Package     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------|

| A 6150  | Voltage and software monitoring     Standby mode: typ. 100 μA     Highly accurate 5 V 100 mA     guaranteed output     Low dropout voltage, typically     250 mV at 100 mA     Unregulated voltage input can     withstand −20 V reverse battery and     +60 V power transients     Regulated voltage accuracy ± 1%     Current limiting     Reset output guaranteed down to     VOUTPUT = 1.2 V     Programmable reset threshold     Voltage reference accuracy ± 3%     Programmable delays for P.O.R.     and W.D. windows     Time base accuracy ± 10%     (over the full temperature range)     ENABLE function     TTL/CMOS compatibility  EN = push-pull: RES = open drain                                                                                                                    | Automotive<br>electronics<br>Cellular<br>telephones<br>Security<br>systems<br>Battery power-<br>ed products<br>High efficiency<br>linear power<br>supply | $3.36 \le V_{INPUT} \le 26 V$                | $175 \mu\text{A} \text{at}$ $V_{\text{INPUT}} = 6 \text{V}$ with $R_{\text{EXT}} = 100 \text{k}\Omega$ | DIP8<br>SO8 |

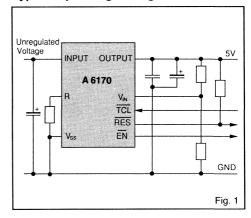

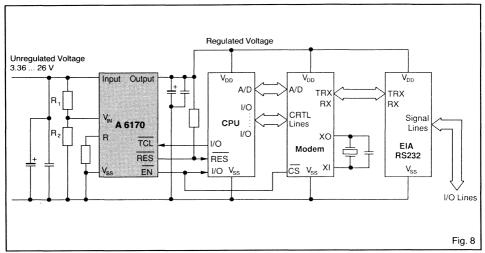

| A 6170  | <ul> <li>Voltage and software monitoring</li> <li>Standby mode: typ. 100 μA</li> <li>Highly accurate 5 V / 100 mA</li> <li>guaranteed output</li> <li>Low dropout voltage, typically</li> <li>250 mV at 100 mA</li> <li>Unregulated voltage input can withstand -20 V reverse battery and +60 V power transients</li> <li>Regulated voltage accuracy ± 1%</li> <li>Current limiting</li> <li>Reset output guaranteed down to V<sub>OUTPUT</sub> = 1.2 V</li> <li>Programmable reset low threshold</li> <li>Voltage window, high threshold 5.9 V</li> <li>Voltage reference accuracy ± 1.5%</li> <li>Programmable delays for P.O.R. and W.D. windows</li> <li>Time base accuracy ± 10%</li> <li>(over the full temperature range)</li> <li>ENABLE function</li> <li>TTL/CMOS compatibility</li> </ul> | Industrial<br>electronics<br>Security<br>systems<br>Telecom<br>systems<br>Hand-held<br>systems<br>High efficiency<br>linear power<br>supply              | $3.36 \le V_{\text{INPUT}} \le 26 \text{ V}$ | 155 $\mu$ A at V <sub>INPUT</sub> = 6 V with R <sub>EXT</sub> = 100 kΩ                                 | DIP8<br>SO8 |

### **Regulator and Surveillance Functions**

| ЕМ Туре                                                        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Applications                                                                                                                                                             | Supply<br>Voltage                            | Typ. Current<br>Consumpt.                                              | Package       |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------|---------------|

| A 6173                                                         | Voltage and software monitoring     3 chip select disable circuits     Standby mode: typ. 100      Highly accurate 5 V / 100 mA     Highly accurate 5 V / 100 mA     Highly accurate 5 V / 100 mA     Unregulated output     Low dropout voltage, typically 250 m X at 100 mA     Unregulated voltage input can withstand − 20 V reverse battery and +60 V power transients     Regulated voltage accuracy ± 1%     Current limiting     Reset output guaranteed down to VoutPut = 1.2 V     Programmable reset low threshold voltage window, high threshold 5.9 V     Voltage reference accuracy ± 1.5%     Programmable delays for P.O.R. and W.D. windows     Time base accuracy ± 10% (over the full temperature range)     ENABLE function     TTL/CMOS compatibility | Industrial<br>electronics<br>Security<br>systems<br>Telecom<br>systems<br>Hand-held<br>systems<br>High efficiency<br>linear power<br>supply                              | $3.36 \le V_{\text{INPUT}} \le 26  \text{V}$ | 155 $\mu$ A at V <sub>INPUT</sub> = 6 V with R <sub>EXT</sub> = 100 kΩ | DIP14<br>SO14 |

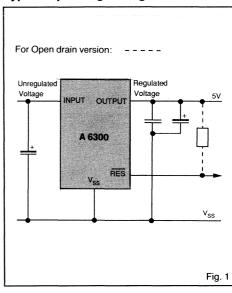

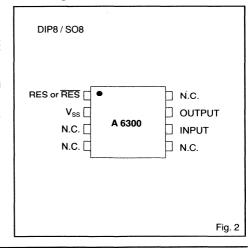

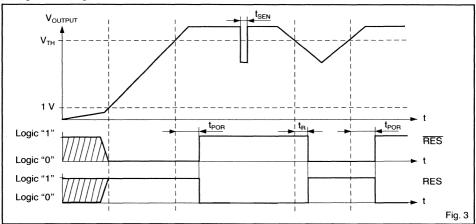

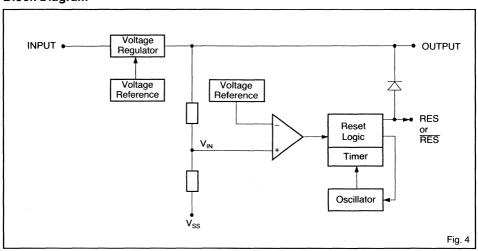

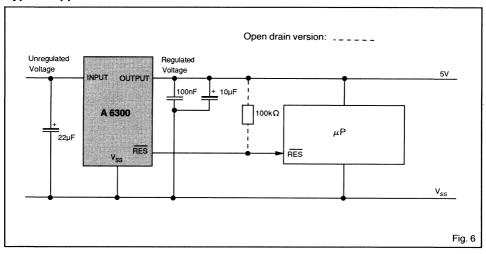

| A 6300                                                         | Voltage monitoring Low current consumption: typ. 100 µA Highly accurate 5 V/100 mA guaranteed output Low dropout voltage, typically 250 mV at 100 mA Unregulated voltage input can withstand -20 V reverse battery and +60 V power transients Regulated voltage accuracy ± 1% Current limiting Reset output guaranteed down to V <sub>DD</sub> = 1.0 V Clear microprocessor start on power-up On-chip oscillator, no external components required                                                                                                                                                                                                                                                                                                                          | Automotive<br>electronics<br>Industrial<br>electronics<br>Security<br>systems<br>Telecom<br>systems<br>Hand-held<br>systems<br>High efficiency<br>linear power<br>supply | $2.3 \le V_{INPUT} \le 26 V$                 | 100 µA at<br>V <sub>INPUT</sub> = 6 V                                  | DIP8<br>SO8   |

| AA<br>AB<br>AC<br>AD<br>AG<br>AH<br>AI<br>AK<br>AN<br>AO<br>AQ | 3.5 V <sup>1)</sup> 4.0 V <sup>1)</sup> • Reset active high, push-pull 2.0 V <sup>1)</sup> 2.4 V <sup>1)</sup> 3.5 V <sup>1)</sup> 4.0 V <sup>1)</sup> • Reset active low, open drain 2.0 V <sup>1)</sup> 2.4 V <sup>1)</sup> 2.8 V <sup>1)</sup> 3.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                          |                                              |                                                                        |               |

<sup>1)</sup> Non-stock items, minimum order 20k pieces

### Interface

| ЕМ Туре              | Features                                                                                                                                                                                                                                                                                                                                          | Applications                                                | Supply<br>Voltage                                                                                     | Typ. Current<br>Consumption                                                                                                                                                                                                                                                                                                                                                                                              | Package       |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

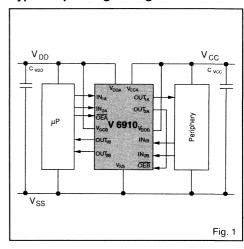

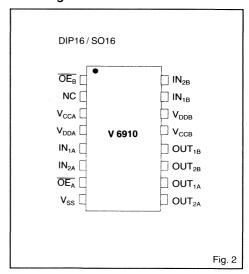

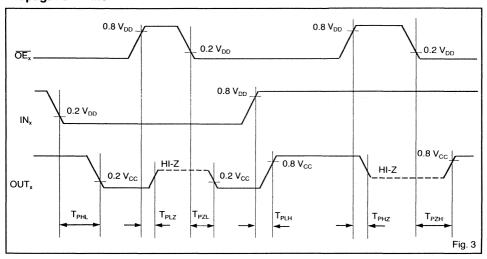

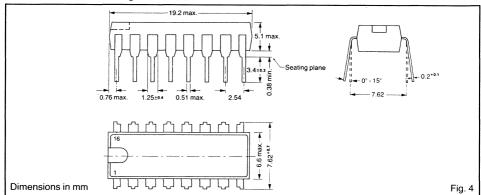

| V 6910 <sup>1)</sup> | DUAL Two Channel Level Shifter     4 separated input / output power supplies     4 inputs (TTL compatible)     2 Output Enable control     Standby current:     typ. 100 nA at V <sub>DD</sub> = V <sub>CC</sub> 10 V     Maximum frequency 8 MHz     TTL/CMOS compatibility  Open drain output Push-pull output                                  | Industrial<br>electronics<br>Battery<br>powered<br>products | $\begin{array}{l} 1.5 \leq V_{DD} \leq 10 \text{ V} \\ 1.5 \leq V_{CC} \leq 10 \text{ V} \end{array}$ | $\begin{array}{l} I_{DD}\left(1.5\text{V}\right)=4\mu\text{A}\text{ and }\\ I_{CC}\left(1.5\text{V}\right)=40\mu\text{A}\text{ at }\\ 500\text{kHz}\text{ on the inputs} \\ I_{DD}\left(10\text{V}\right)=40\mu\text{A}\text{ and }\\ I_{CC}\left(10\text{V}\right)=1.2\text{mA}\text{ at }\\ 500\text{kHz}\text{ on the inputs} \end{array}$                                                                            | DIP16<br>SO16 |

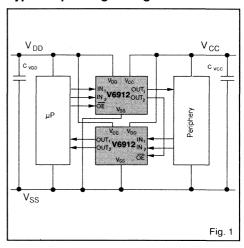

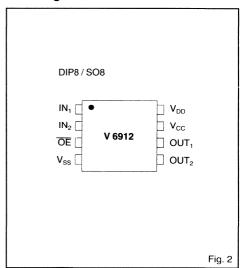

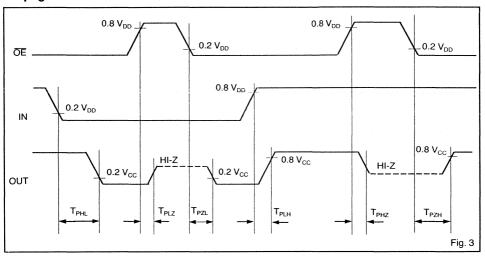

| V 6912 1)            | Two Channel Level Shifter see 2 separated input/output power supplies plant (TTL compatible) Output Enable control Standby current: typ. 50 nA at V <sub>DD</sub> = V <sub>CC</sub> 10 V Maximum frequency 8 MHz TTL/CMOS compatibility                                                                                                           | Industrial<br>electronics<br>Battery<br>powered<br>products | $1.5 \le V_{DD} \le 10 \text{ V}$<br>$1.5 \le V_{CC} \le 10 \text{ V}$                                | $I_{DD}$ (1.5 V) = 2 $\mu$ A and $I_{CC}$ (1.5 V) = 20 $\mu$ A at 500 kHz on the inputs $I_{DD}$ (10 V) = 20 $\mu$ A and $I_{CC}$ (10 V) = 600 $\mu$ A at 500 kHz on the inputs                                                                                                                                                                                                                                          | DIP8<br>SO8   |

| 10<br>20             | Open drain output<br>Push-pull output                                                                                                                                                                                                                                                                                                             |                                                             |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

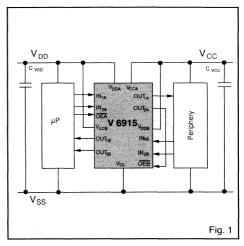

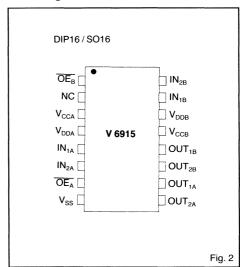

| V 6915 <sup>1)</sup> | DUAL Two Channel Level Shifter     4 separated input / output power supplies     4 inputs with Schmitt Trigger     2 Output Enable control     High noise immunity     Standby current:     typ. 100 nA at V <sub>DD</sub> = V <sub>CC</sub> 10 V     Maximum frequency 5 MHz     Output CMOS compatibility  Open drain output  Death and noutput | Industrial<br>electronics<br>Battery<br>powered<br>products | $\begin{array}{l} 1.5 \leq V_{DD} \leq 10  V \\ 1.5 \leq V_{CC} \leq 10  V \end{array}$               | $\begin{array}{l} I_{DD}\left(1.5\mathrm{V}\right) = 4\mu\mathrm{A}~\mathrm{and}\\ I_{CC}\left(1.5\mathrm{V}\right) = 40\mu\mathrm{A}~\mathrm{at}\\ 500~\mathrm{kHz}~\mathrm{on}~\mathrm{the}~\mathrm{inputs} \\ I_{DD}\left(10\mathrm{V}\right) = 60\mu\mathrm{A}~\mathrm{and}\\ I_{CC}\left(10\mathrm{V}\right) = 1.2~\mathrm{mA}~\mathrm{at}\\ 500~\mathrm{kHz}~\mathrm{on}~\mathrm{the}~\mathrm{inputs} \end{array}$ | DIP16<br>SO16 |

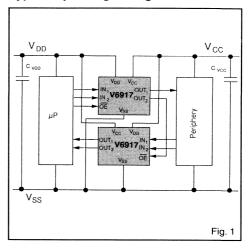

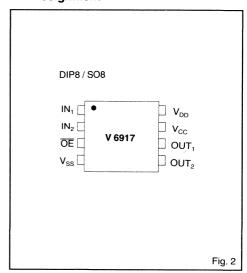

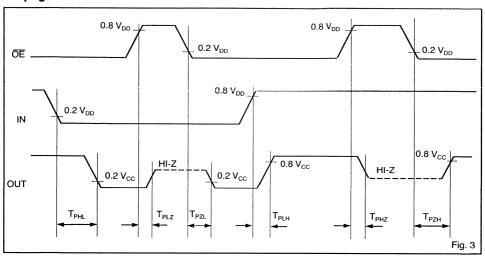

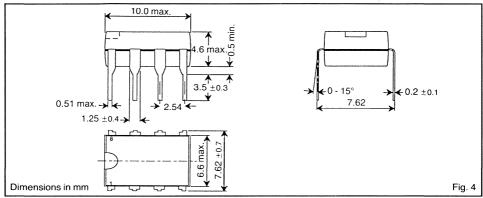

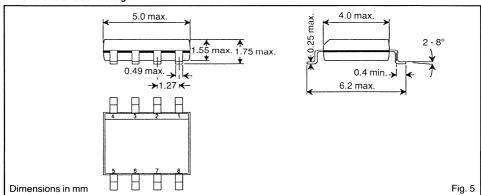

| V 6917 1)            | Push-pull output  Two Channel Level Shifter 2 separated input / output power supplies 2 inputs with Schmitt Trigger Output Enable control High noise immunity Standby current: typ. 50 nA at V <sub>DD</sub> = V <sub>CC</sub> 10 V Maximum frequency 5 MHz Output CMOS compatibility                                                             | Industrial<br>electronics<br>Battery<br>powered<br>products | $1.5 \le V_{DD} \le 10 \text{ V}$<br>$1.5 \le V_{CC} \le 10 \text{ V}$                                | $I_{DD}(1.5 \text{ V}) = 2 \mu\text{A}$ and $I_{CC}(1.5 \text{ V}) = 20 \mu\text{A}$ at 500 kHz on the inputs $I_{DD}(10 \text{V}) = 30 \mu\text{A}$ and $I_{CC}(10 \text{V}) = 600 \mu\text{A}$ at 500 kHz on the inputs                                                                                                                                                                                                | DIP8<br>SO8   |

| 10<br>20             | Open drain output<br>Push-pull output                                                                                                                                                                                                                                                                                                             |                                                             |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

<sup>1)</sup> Non-stock items, minimum order 50k pieces

### **Contactless Identification Devices (CID)**

| ЕМ Туре                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Applications                                                                               | Supply<br>Voltage                          | Typ. Current<br>Consumpt. | Package |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------|---------|

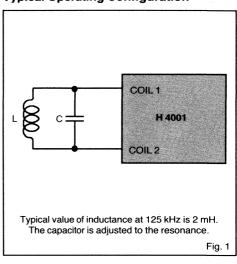

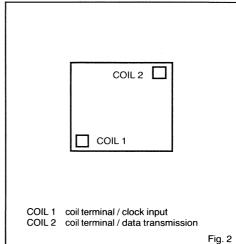

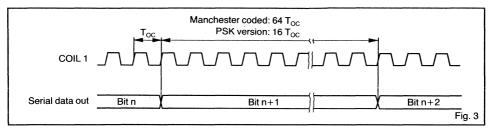

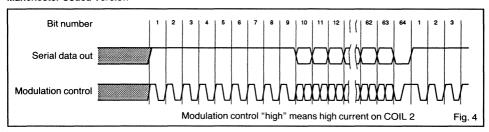

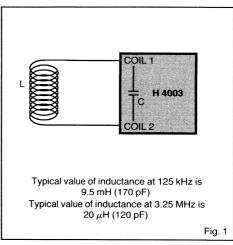

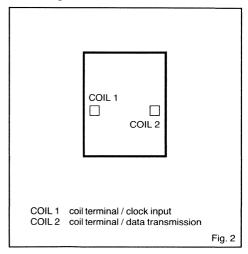

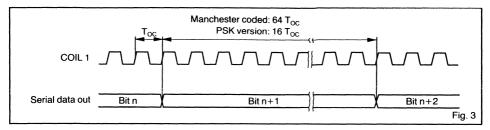

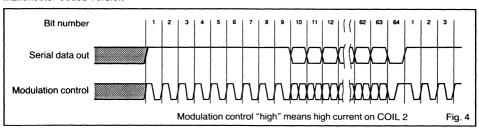

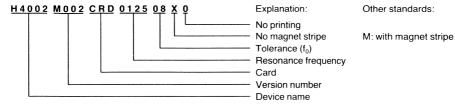

| H 4001                                           | Read-only contactless identification IC     64-bit memory array, laser programmable     Full wave rectifier     Voltage limiter     Data transmission by amplitude modulation     Manchester or PSK coding                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Industrial<br>transponder<br>Car immobilizer<br>Animal<br>identification<br>Access control | Supplied via<br>electroma-<br>gnetic field |                           | ·       |

| H 4003                                           | Read-only contactless identification IC     64-bit memory array, laser programmable     Full wave rectifier     Voltage limiter     Data transmission by amplitude modulation     Manchester or PSK coding     170 pF ± 2% resonant C on chip                                                                                                                                                                                                                                                                                                                                                                                                                 | ISO format<br>contactless<br>identification<br>cards                                       | Supplied via<br>electroma-<br>gnetic field |                           |         |

| Contact-<br>less<br>Button<br>125 kHz            | This contactless button is an application of the H 4001  • Material: mix PUR / mat PVC on both sides • Colour: white • Outside dimensions: 28 mm diam. x 1.5 mm thick • Temperature stability: -35 to +60°C • Electronic characteristics: - EM H 4001, 64 bit read-only integrated circuit - Manchester code - Coil, L = 2 mH ± 3% - Chip capacitor, C = 820 pF ± 5% • Resonance frequency: 125 kHz ±10% • Typical reading distance: 0 to 180 mm depending on reader performance and coil characteristics  On request: • Resonant frequency tolerance ± 5% • PSK code                                                                                         | Access control Identification systems                                                      |                                            |                           |         |

| ISO -<br>Contact-<br>less<br>Chipcard<br>125 kHz | This contactless chip-card is an application of the H 400x  • Material: mix PUR / bright PVC on both sides  • Colour: white  • Physical characteristics:  - Dimensions, bending and torsion properties according to ISO norm 7816-1  - Temperature stability: – 35 to +50°C  • Electronic characteristics:  - EM H 400x, 64 bit read-only integrated circuit  - Manchester code  • Resonant frequency: 125 kHz ±8%  • Typical reading distance: 0 to 500 mm depending on reader performance and coil characteristics  On request:  • Both sides of the card can be printed according to customer requirements  • Resonant frequency tolerance ±3%  • PSK code | Access control Identification systems                                                      |                                            |                           |         |

### **EMS Mixed-Mode Arrays**

| ЕМ Туре                                | Description<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Applications                                                   | Supply<br>Voltage      | Gate<br>Complex.                                   | Package                                                                                                              |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| V 83nn <sup>2)</sup>                   | EMS V8300 Series is a family of transistor arrays for analog/digital applications, with limited capability in the analog domain. Its internal organization is based on a "Sea-of-Gates" architecture offering a high degree of design flexibility and performance. This series is especially suitable for low-voltage, low-power digital applications. It is aimed to cost-effectively satisfy the digital and mixed-mode circuit requirements of up to 6,000 gate complexity.  Mixed analog-digital family  2 μ Double-metal, low-voltage CMOS technology  Low power dissipation  Typical gate delay of 1.6 ns at C = 0.1 pF, 4.5 V, 85°C  Low power quartz oscillator  Fast turn-around time  Low development cost                                                                                                   | Industrial<br>control and<br>automation<br>Consumer<br>Medical | $1 \le V_{DD} \le 6V$  |                                                    | DIL8 to DIL64<br>SO8 to SO32<br>PLCC20 to PLCC84<br>QFP44 to QFP128<br>Chip form and<br>other packages<br>on request |

| 06<br>09<br>12<br>16<br>20<br>23<br>26 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                |                        | 300<br>700<br>1300<br>2600<br>4000<br>5200<br>6800 | 24<br>36<br>48<br>64<br>80<br>92                                                                                     |

| V 84nn <sup>2</sup> )                  | EMS V8400 Series is a family of arrays designed to meet mixed analog-digital circuit requirements. In addition to their "Sea-of-Gates" core, a dedicated analog array field is added, consisting of passive elements such as resistors, capacitors, lateral pnp's and long-channel transistors. A fully integrated, low-power amplitude-regulated quartz oscillator and a temperature compensated bandgap voltage reference are available. Due to its specific architecture, the EMS V8400 Series offers an excellent performance in mixed mode applications. Mixed analog-digital family  2μ Double-metal, low-voltage CMOS technology  Low power dissipation  Typical gate delay of 1.6 ns at C = 0.1 pF, 4.5 V, 85°C  Temperature compensated voltage reference  Low power quartz oscillator  Fast turn-around time | Industrial<br>control and<br>automation<br>Consumer<br>Medical | $1 \le V_{DD} \le 6 V$ |                                                    | DIL8 to DIL64 SO8 to SO32 PLCC20 to PLCC84 QFP44 to QFP128 Chip form and other packages on request                   |

| nn <sup>2)</sup> 06 09 12 16 20 23 26  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                |                        | 190<br>590<br>1000<br>2300<br>3400<br>4700<br>6300 | Pads  24  36  48  64  80  92 104                                                                                     |

<sup>2)</sup> n or nn stands for the version

|     |                                           | Page |

|-----|-------------------------------------------|------|

| 1.  | Management Responsibility                 | 2-4  |

| 2.  | Quality System                            | 2-4  |

| 3.  | Contract Review                           | 2-4  |

| 4.  | Design Control                            | 2-4  |

| 5.  | Document Control                          | 2-5  |

| 6.  | Purchasing                                | 2-5  |

| 7.  | Purchaser Supplied Product                | 2-5  |

| 8.  | Product Identification and Traceability   | 2-5  |

| 9.  | Process Control                           | 2-5  |

| 0.  | Inspection and Testing                    | 2-5  |

| 11. | Inspection, Measuring and Test Equipment  | 2-6  |

| 2.  | Inspection and Test Status                | 2-6  |

| ١3. | Control of Non-Conforming Product         | 2-6  |

| ١4. | Corrective Actions                        | 2-6  |

| 15. | Handling, Storage, Packaging and Delivery | 2-6  |

| ۱6. | Quality Records                           | 2-6  |

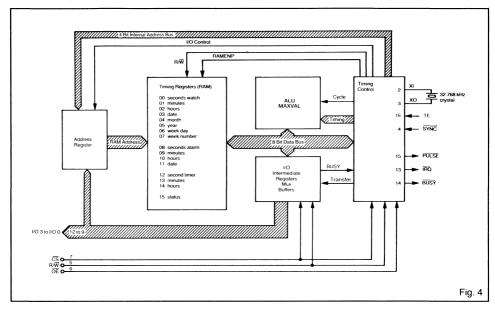

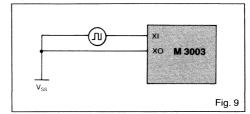

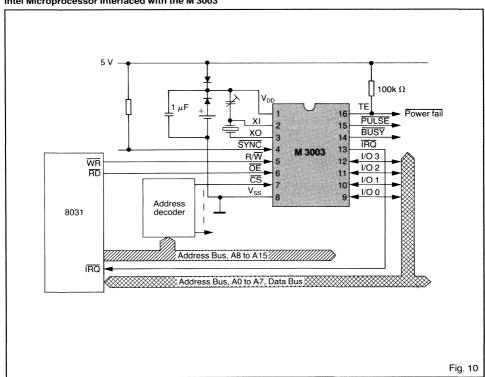

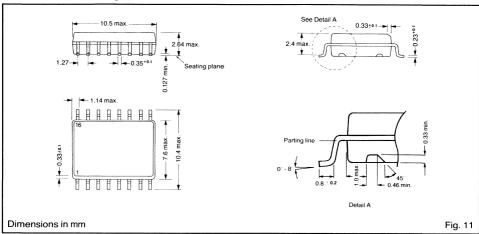

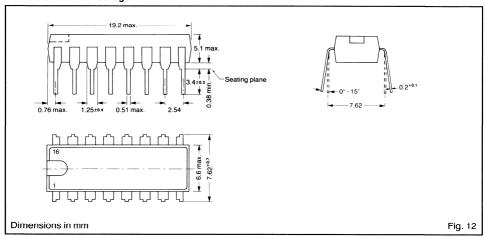

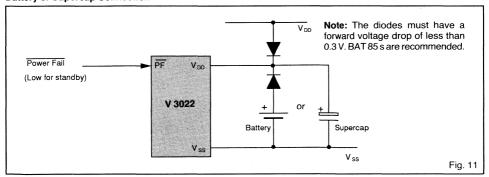

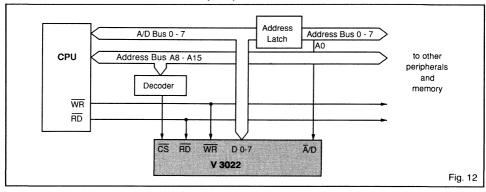

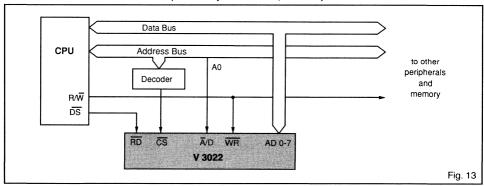

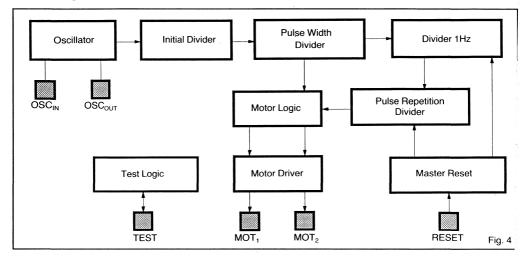

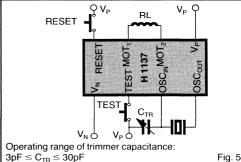

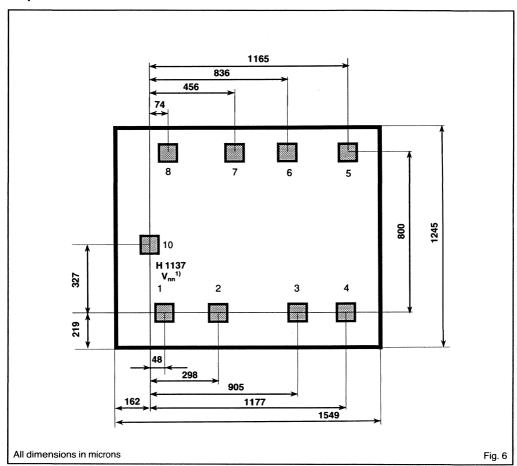

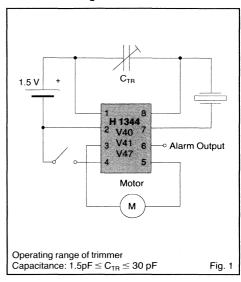

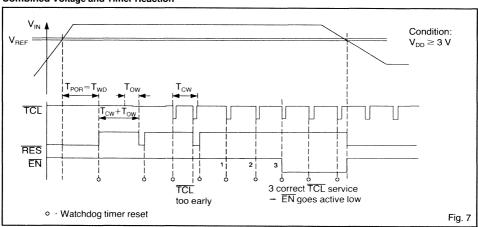

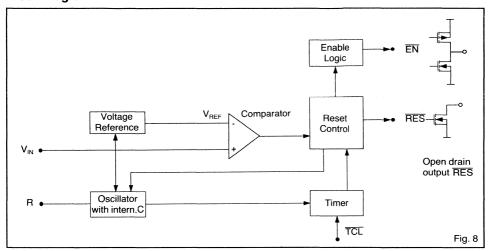

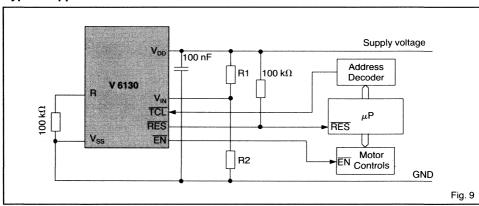

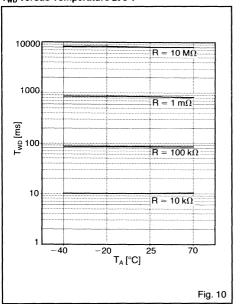

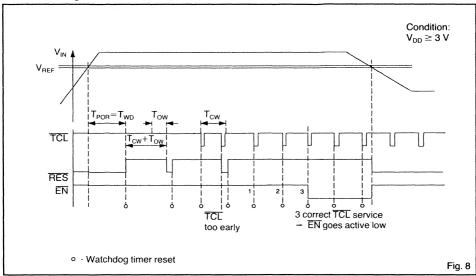

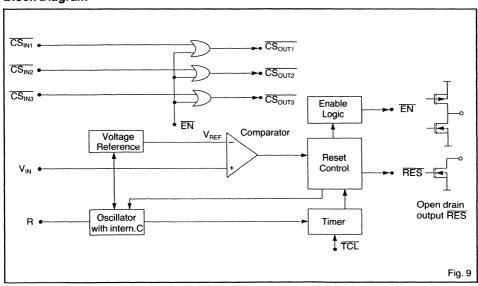

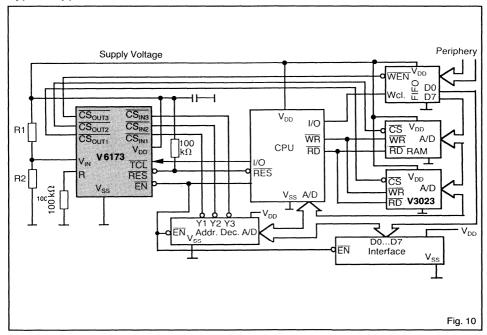

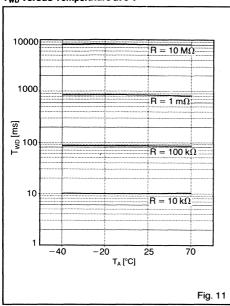

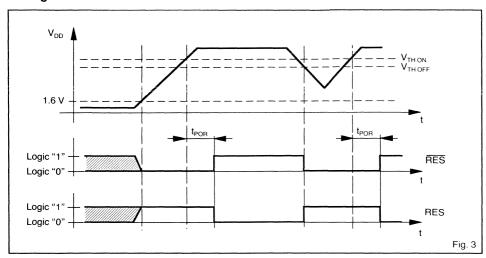

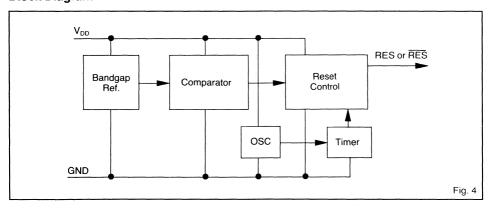

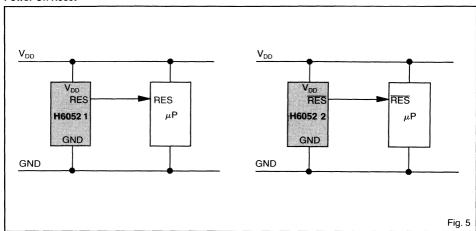

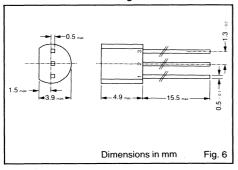

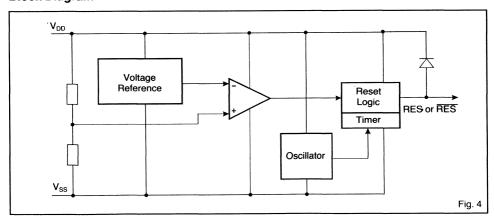

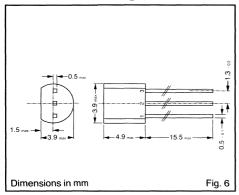

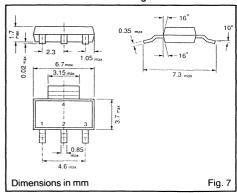

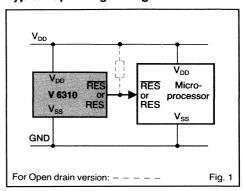

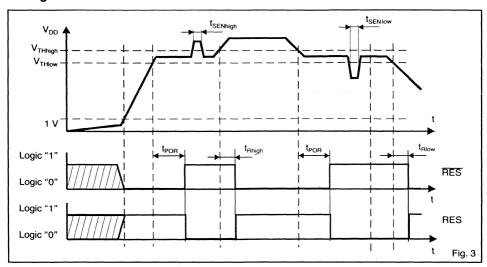

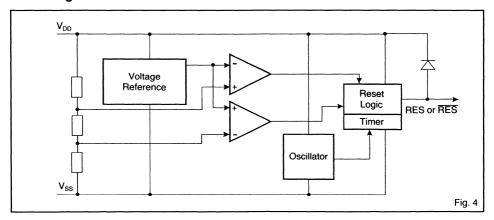

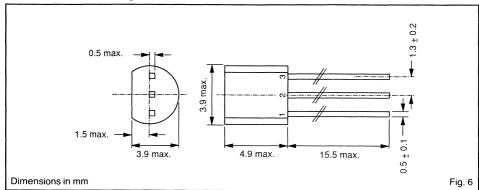

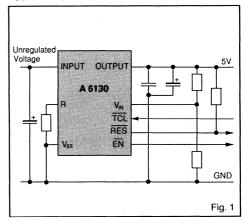

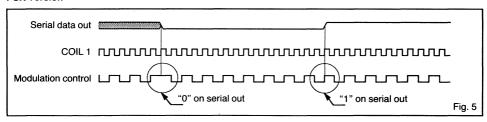

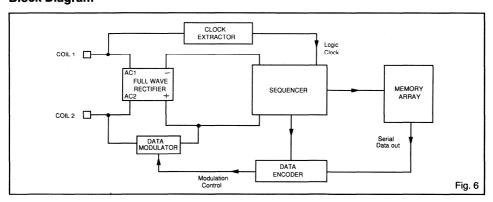

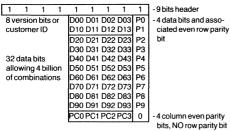

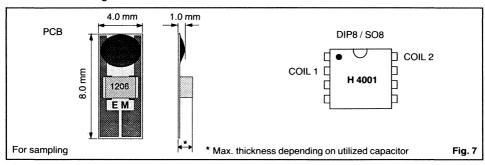

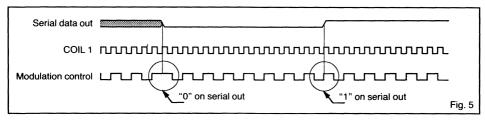

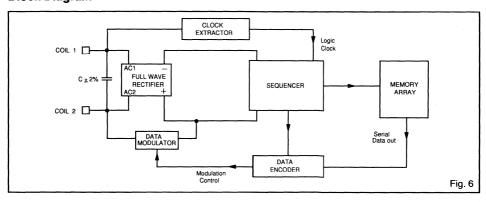

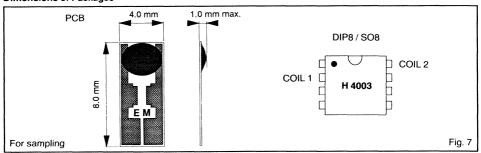

| ١7. | Internal System Audit                     | 2-7  |